Apollo Computing

Laboratories (P) Ltd

mktg@apollocomputing.com

+9140 -27141522 / 27141533

mktg@apollocomputing.com

+9140 -27141522 / 27141533

mktg@apollocomputing.com

+9140 -27141522 / 27141533

mktg@apollocomputing.com

+9140 -27141522 / 27141533

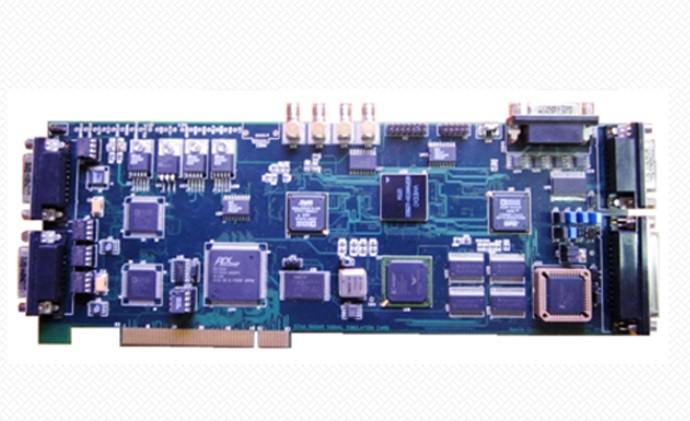

The board consists of two DSP processors which will process the incoming analog signals. Control logic is implemented in FPGA. The incoming analog signals are received by the dual analog to digital converters. These digital converted analog signals can be communicated to DSPs and also to the host system. Interfacing with the host system is through a PCI bridge. FPGA can also be used for transmitting data either through serial communication or by parallel way. The selection of the mode of communication is by a hardware jumper. PCI-9054 is used for interfacing local bus to host bus.

Ordering Information:

For specific Configurations / Specifications Consult ACL for further details