CCPMC Bus Based

MIL-STD-1553B

BCRTMT & MRTBCMT Modules

MIL-STD-1553B is the military specification defining a Digital Time Division Command/Response Multiplexed Data Bus. The 1553 databus is a dual-redundant, bi- directional, Manchester II encoded databus with a high bit error reliability. The Products Support Many Options. Contact us for More details

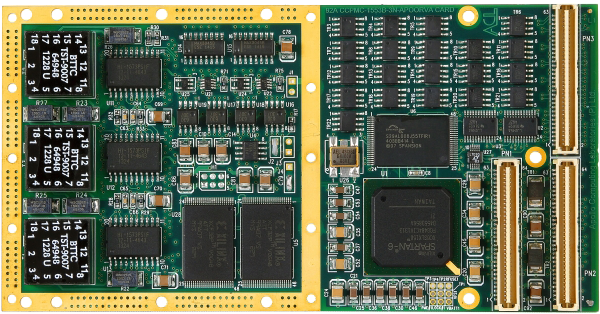

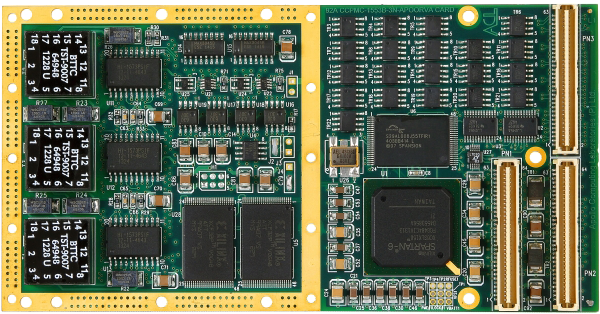

CCPMC Based APOORVA-1553B Three Node BCRTMT Add On Card

Overview

CCPMC-1553B-3Node PMC module is based on ACL's APOORVA IP core and Spartan-6 FPGA.BC/RT/MT Bus Controller (BC), Remote Terminal (RT) and Monitor Terminal (MT) modes are independently supported on each channel of the PMC-1553B-3Node module.

Introduction

The CCPMC-1553B-3Node provides three dual-redundant MIL-STD-1553B interfaces along with Eight RS-422 channels on a PMC/CCPMC module.It complements ACL's latest generation of PowerPC-750 based SBC with dual PMC/CCPMC sites.The CCPMC-1553B-3Node comes with VxWorks libraries.To provide full testability, the CCPMC-1553B-3 Node is supplied with Built-In-Test (BIT). BIT software routines, which provides diagnostics to give confidence in the sub-system integration.The product is available in standard air-cooled level as well as Conduction Cooled versions.

Technical Features

Salient Technical Features:

-

- 32-bit/33 MHZ PMC

-

- Three dual redundant BC/RT/MT MIL-STD-1553B interfaces

-

Transformer coupled interfaces

-

Supports PCI interrupts

-

External BC trigger / RT status brought out

-

Eight RS-422 channels

-

Current and temparature monitoring

-

VxWorks Libraries

-

Available in Air-cooled and Conduction Cooled Versions

BC / RT / MT Operation

Each channel may be independently programmed for BC, RT, or RT/MT mode. This option makes use of the ACL's APOORVA IP core to provide full support for all modes of operation. When used with ACL's APOORVA IP core, 4K words of memory is available for message preparation and double buffering etc.

BC mode includes advanced features such as bulk-data transfers, frame auto-repeat, automatic retries on the same channel or bus switching on alternate channel, programmable gap times etc

RT mode supports all advanced features including single buffering, double buffering, sub-address circular buffering, programmable command illegalisation and Busy etc.

MT modes allows all standard features including word monitoring, selective message monitoring etcSimultaneous RT / monitor mode is also supported as it is required some times for backup BC terminals.

Hard-warable and Software Programmable RT Addressing

The RT address of each channel on the CCPMC-1553B-3Node may be set by Library functions. RT address is also settable through Hardware settings as per notice-2 features. In this mode the software addressing is disabled.

BC Trigger / RT Status

An external trigger line is provided for each channel to allow hardware control of the BC. Messages may be pre-programmed, and then the BC can start from the point the trigger signal is activated.In RT mode this line becomes a sub-system status line, used to indicate a failure within the sub-system.

RS-422 Channels

The CCPMC-1553B-3Node module is supported with Eight RS-422 channels. A number of software routines are provided in VxWorks environment, to access and utilize each and every features of on-board serial controller chip.

Software Support

ACL provides CCPMC-1553B-3Node with driver and library software for VxWorks operating system environment to assist in software development.

On requirement basis libraries and driver software for other Operating Systems can be provided.

-

PMC-1553B-1N: Single Node PMC 1553B Module with RS-422

-

PMC-1553B-2N: Two Node PMC 1553B Module with RS-422

-

PMC-1553B-3N: Three Node PMC 1553B Module with RS-4223

Ordering Information

-

PMC-1553B-1N: Single Node PMC 1553B Module with RS-422

-

PMC-1553B-2N: Two Node PMC 1553B Module with RS-422

-

PMC-1553B-3N: Three Node PMC 1553B Module with RS-422

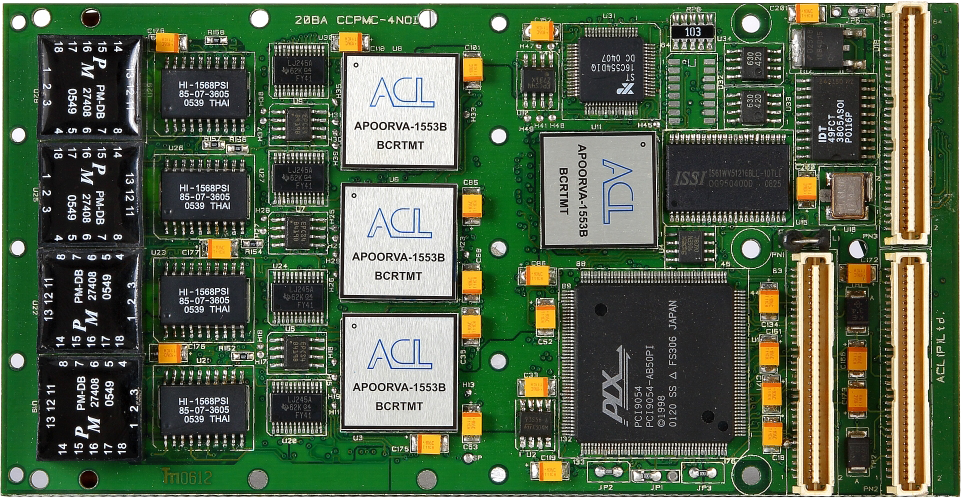

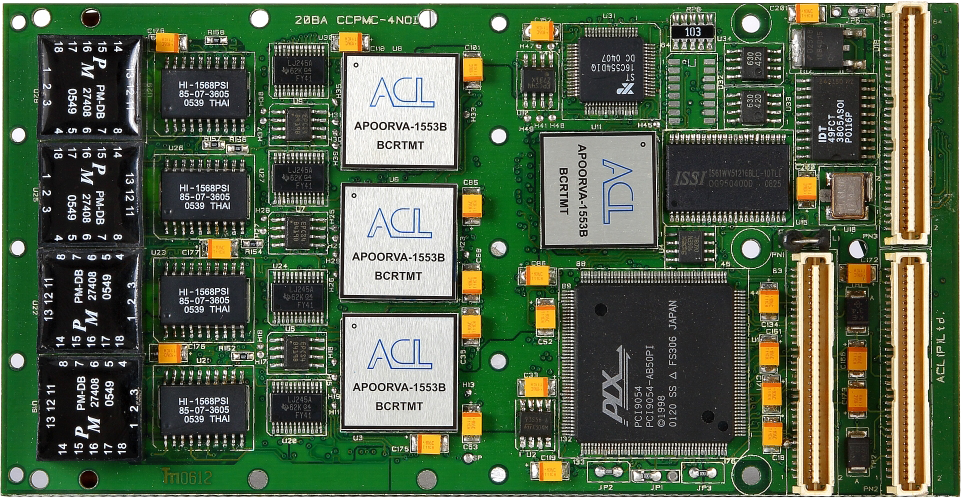

CCPMC Based APOORVA-1553B

Four Node BCRTMT Add On Card

Overview

The APOORVA-1553B Based BCRTMT is a CCPMC Four Node MIL-STD-1553B interface card which can be hosted by any SBC with PMC sites. The CCPMC card provides up to Four independently configurable buses. Each Bus provides simultaneously dual redundant BC/RT/MT or BC, RT & MT (based on ACL’s APOORVA-1553B Core) concurrently conforming to MIL-STD-1553B Notice-2. The design supports multiple modules on single SBC - limitations being: available system free CCPMC sites and computational power of the Computer. Thus, the APOORVA-CCPMC-FOUR-BCRTMT-1553B is an excellent choice for dynamic real-time avionics simulations. The on-board double buffered dual port memory facilitates parallel message preparation & transfers, increasing the effective throughput.

The APOORVA-1553B Based BCRTMT module comes with Real Time Operating System (RTOS) Bus Libraries, powerful C-callable library routines to access the bus at various levels of abstraction, hardware complexities being transparent to the user. The performance of APOORVA-1553B Based BCRTMT is far superior to solutions offered by others around the globe.

Apoorva provides a unique facility to the user to enable or disable the messages in the Frame.

Technical Features

-

Up to Four independently configurable buses. Each Bus provides simultaneously dual redundant BC/RT/MT or BC, RT & MT nodes (based on options chosen) conforming to MIL-STD-1553B Notice-2.on one system free CCPMC site.

-

Supports full MIL-STD-1553B Notice-2.

-

Supports all 1553B message formats and mode-codes.

-

On board time-tag counter.

-

RT Sub-address circular buffers to support bulk data transfers.

-

Optional separation of RT broadcast data.

-

- Each channel supports double buffered dual ported 7.5 K X 16 bit memory for preparation and transfer.

-

Programmable RT address.

-

High performance.

-

Two on-board timers.

-

Typical Inter-message gap of 10 micro seconds. Optionally 4.20 micro seconds.

-

Scalable architecture supporting intra system expandability.

-

Supports multiple bus simulation on single Computing system.

-

Ideal for real-time avionics simulation.

-

Bus Libraries: Powerful C-callable routines to support BC/RT/MT or BC, RT & MT functions.

-

Powerful message debugging facility.

-

Unprecedented Flexibility: Minor Frame Time Programmable in steps of 1.0 milli seconds accurately along with Minor frame messages loadable in hardware itself to provide accurate real-time performance.

-

Built in Diagnostic and test S/W for diagnostics.

-

Real Time OS Bus Libraries.

MEMORY

| As BC

|

7.5 K words |

| As RT

|

7.5 K words |

| As MT

|

16 K words |

| Circular Buffer

|

15 K words |

With the APOORVA-1553B Based BCRTMT module,

the following Errors can be injected to verify the LRUs and other systems functionin

| Manchester errors |

Bi-phase errors |

| Bit length errors |

Sync errors |

| Word count errors |

Gap time introduction etc. |

Bus Information

-

The APOORVA-1553B Based BCRTMT CCPMC module comes with C-callable library functions/routines to utilise the resources of the module.

-

APOORVA-CCPMC-ONE-BC, RT & MT-1553B:CCPMC bus based MIL-STD-1553B One Node Module supporting BC, RT & MT (simultaneously).

-

APOORVA-CCPMC-TWO-BC, RT & MT-1553B:CCPMC bus based MIL-STD-1553B Two Node Module supporting BC, RT & MT (simultaneously) for each bus.

-

APOORVA-CCPMC-ONE-BC/RT/MT-1553B:CCPMC bus based MIL-STD-1553B One Node BC/RT/MT Module.

-

APOORVA-CCPMC-TWO-BC/RT/MT-1553B:CCPMC bus based MIL-STD-1553B Two Node BC/RT/MT Module.

-

APOORVA-CCPMC-THREE-BC, RT & MT-1553B:CCPMC bus based MIL-STD-1553B Three Node Module supporting BC, RT & MT (simultaneously).

-

APOORVA-CCPMC-FOUR-BC, RT & MT-1553B:CCPMC bus based MIL-STD-1553B Four Node Module supporting BC, RT & MT (simultaneously) for each bus.

-

APOORVA-CCPMC-THREE-BC/RT/MT-1553B:CCPMC bus based MIL-STD-1553B Three Node BC/RT/MT Module.

-

APOORVA-CCPMC-FOUR-BC/RT/MT-1553B:CCPMC bus based MIL-STD-1553B Four Node BC/RT/MT Module.

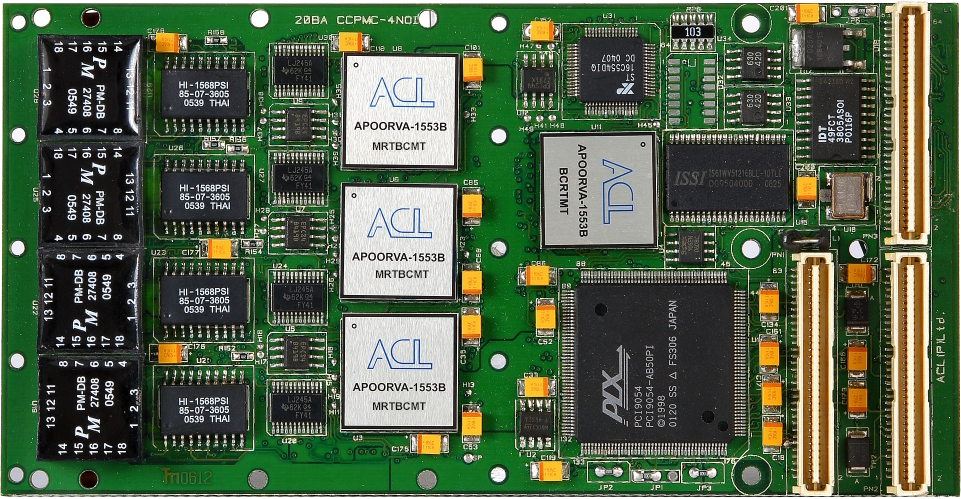

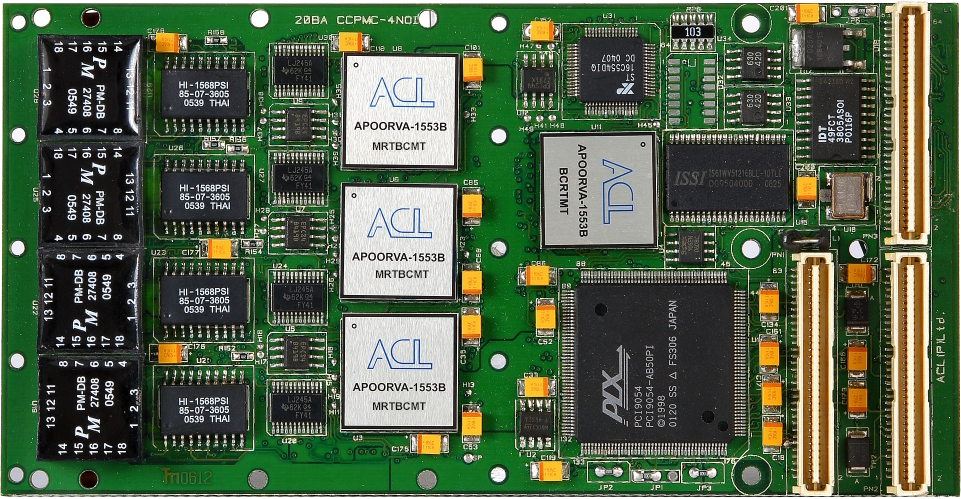

CCPMC Based APOORVA-1553B Four Node MRTBCMT Add On Card

Overview

The APOORVA-1553B Based MRTBCMT is a CCPMC Four Node MIL-STD-1553B card and can be hosted by any standard single board computer with CCPMC sites providing simultaneously Four buses each with dual redundant 31RTs, BC & MT (based on ACL’s Apoorva-1553B Core) concurrently conforming to MIL-STD-1553B Notice-2. The design supports a single SBC hosting multiple modules - limitations being: available CCPMC sites and computational power of SBC. Thus, the APOORVA-1553B Based MRTBCMT is an excellent choice for dynamic real-time avionics simulations. The on-board double buffered dual port memory facilitates parallel message preparation & transfers, increasing the effective throughput.

The APOORVA-1553B Based MRTBCMT module comes with Real Time Operating System (RTOS) Bus Libraries, powerful C-callable library routines to access the bus at various levels of abstraction, hardware complexities being transparent to the user. The performance of APOORVA-1553B Based MRTBCMT is far superior to solutions offered by others around the globe.Apoorva provides a unique facility to the user to enable or disable the messages in the Frame.

Technical Features

-

Provides simultaneously up to Four buses each with dual redundant 31RTs, BC & MT (based on ACL’s APOORVA-1553B Core) conforming to MIL-STD-1553B Notice-2 on one free CCPMC site.

- Supports full MIL-STD-1553B Notice-2.

-

Supports all 1553B message formats and mode-codes.

-

On board time-tag counter.

-

RT Sub-address circular buffers to support bulk data transfers.

-

- Optional separation of RT broadcast data.

-

Each channel supports double buffered dual ported 7.5 K X 16 bit memory for preparation and transfer.

-

Programmable RT address.

-

High performance.

-

Scalable architecture supporting intra system expandability.

-

Supports multiple bus simulation on single Computing system.

-

Ideal for real-time avionics simulation.

-

Built in test S/W for diagnostics.

-

Bus Libraries: Powerful C-callable routines to support BC, RT & MT functions.

-

Powerful message debugging facility.

-

Unprecedented Flexibility: Minor Frame Time Programmable in steps of 1.0 milli seconds accurately along with Minor frame messages loadable in hardware itself to provide accurate real-time performance.

-

- Typical Inter-message gap of 10 micro seconds.

-

- Real Time OS Bus Libraries.

MEMORY

| As BC

|

7.5 K words |

| As RT

|

7.5 K words |

| As MT

|

16 K words |

| Circular Buffer

|

256 K words |

With the APOORVA-1553B Based MRTBCMT module,

the following Errors can be injected to verify the LRUs and other systems functioning:

| Manchester errors |

Bi-phase errors |

| Bit length errors |

Sync errors |

| Word count errors |

Gap time introduction etc. |

Bus Libraries

- The APOORVA-CCPMC-MRT-BC-MT-1553B CCPMC bus based module comes with C-callable library functions/routines to utilise the resources of the module.

Ordering Information

-

APOORVA-CCPMC-ONE-MRT-BC-MT-1553B: CCPMC bus based MIL-STD-1553B Simulator / tester Module providing Simultaneous 31RTs, BC & MT on One 1553B bus

-

APOORVA-CCPMC-TWO-MRT-BC-MT-1553B: CCPMC bus based MIL-STD-1553B Simulator / tester Module providing Simultaneous 31RTs, BC & MT on Two 1553B buses

-

APOORVA-CCPMC-THREE-MRT-BC-MT-1553B: CCPMC bus based MIL-STD-1553B Simulator / tester Module providing Simultaneous 31RTs, BC & MT on Three 1553B buses

-

APOORVA-CCPMC-FOUR-MRT-BC-MT-1553B: CCPMC bus based MIL-STD-1553B Simulator / tester Module providing Simultaneous 31RTs, BC & MT on Four 1553B buses

mktg@apollocomputing.com

+9140 -27141522 / 27141533

mktg@apollocomputing.com

+9140 -27141522 / 27141533

mktg@apollocomputing.com

+9140 -27141522 / 27141533

mktg@apollocomputing.com

+9140 -27141522 / 27141533